发布时间:2025-07-23 来源:闪德资讯

01DDR4开始放量

受惠DDR4现货价格自5月以来明显上涨,带动合约价谈判转为卖方市场。相关产品线第三季起报价上扬,订单需求强劲,下半年营运动能持续升温。华邦电DDR4市场以8GB与16GB产品涨幅最为明显,8GB DDR4下半年开始放量。DDR4与LPDDR4现阶段处于高需求状态,能见度已至第四季。

产能方面,现阶段DDR4产品多数采用20纳米工艺制程,仍具有市场竞争力。下一代16纳米工艺制程已进入准备阶段,预计2026年第一季至第二季放量。随着原厂退出DDR4市场,供需缺口可望维持一至两年。非PC、手机一般消费性产品搭配DDR4更实惠,因DDR5入门容量为16GB。在供不应求态势下,DDR4报价优势可持续多个季度。

02 NAND原厂加速升级

NAND Flash技术朝向高密度、大容量TLC/QLC加速迭代,256Gb及以下容量NAND产出同步大幅收缩,部分产品已逐步进入停产状态。缺乏其他替代方案情况下,NAND原厂加速推动低容量嵌入式产品升级储存配置。目前32GB及以下容量eMMC产品应用相当分散,下游涵盖车载后装、智能音箱、POS机、机器人、机顶盒、投影机、电视、VR装置等多个领域。尽管部分高端机型已采用64GB及以上配置,但32GB及以下eMMC仍有市场。随着供应端策略调整,低容量嵌入式产品NAND供应逐渐吃紧。

256Gb TLC NAND Flash现货价格半年内累计涨幅高达近80%,创下近四年新高;MLC NAND现货价较去年底翻倍上涨。相较NAND原厂紧缩管控,512Gb NAND Wafer价格相对稳定。512Gb TLC NAND Flash晶圆价格第一季度末略有调升后,第二季以来保持平稳趋势。256Gb与512Gb TLC NAND之间差价已大幅缩小至0.3美元,带动相关嵌入式成品现货价格同步攀升。目前16GB/32GB/64GB eMMC现货价格几乎处于相同水平。业内认为,随着低容量eMMC产品供应减少,库存消耗渐趋完成,16GB eMMC可能比32GB价格更高。供应商将通过高容量产品降规,解决供应问题,供应低容量嵌入式产品,避免出现价格倒挂。NAND原厂仍持续加速推动嵌入式容量升级,也考验终端客户定价策略。

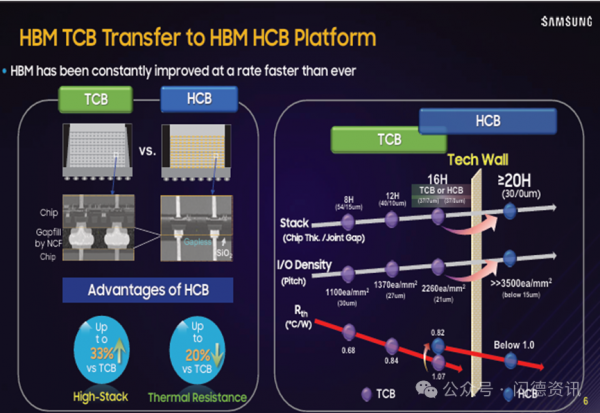

03 三星引进混合键合技术

三星电子预计在16层HBM应用混合键合技术。一旦HBM超过16层,现有热压(TC)键合将无法实现,准备引入混合键合技术。HBM是将多个DRAM垂直堆叠,以提高数据处理速度半导体,TC键合DRAM过程,必不可少的设备。混合键合技术能够消除微凸块(焊球),直接将DRAM连接到铜,减小HBM厚度。三星电子表示,在第7代16层HBM4E同时采用TC键合和混合键合,在第8代20层HBM5全面引入混合键合。

目前最新商业化产品是12层HBM3E。当间距小于15微米时,必须转向混合键合技术,该技术还具备散热良好优势。

04 DDR6准备量产

在生成式AI、高性能运算(HPC)及数据中心对内存带宽与效率需求大增推动下,新一代内存标准DDR6正式进入发展阶段,朝着量产迈进。预计DDR6 2027年进入大规模导入期。三星、美光与SK海力士全球三大DRAM原厂,率先开启开发计划,围绕DDR6内存芯片、主控与封装模组进行技术验证与产品布局。

根据JEDEC(固态技术协会)推进计划,DDR6规范2024年底完成草案,LPDDR6草案2025年第二季对外发布,2026年进入平台测试与验证阶段。DDR6在性能与架构上有重大突破,起始传输速率达8800MT/s,产品生命周期内最高可达17600MT/s,整体性能比DDR5提升2-3倍。

架构方面DDR6采用4x24bit子通道设计,比DDR5的2x32bit架构在平行处理效率等方面更具优势,但对模组I/O设计与信号完整性要求更高。传统288-pin DIMM插槽难以支持DDR6,由戴尔首创、并经JEDEC推动标准化CAMM2(Compression Attached Memory Module 2)架构,结合高带宽、高密度、低阻抗与薄型化设计,解决传统插槽限制,已有多家厂商已投入相关测试与开发。技术开发方面,三大DRAM原厂已完成DDR6原型芯片设计,与主控厂商及Intel、AMD平台展开接口协同测试。下一代CPU预计2026年支持DDR6,涵盖AI服务器、HPC系统与高端笔记本等领域。业内指出,全球产业链已积极投入模组设计、封装工艺与连接器技术创新,抢占高性能运算市场。

05 力积电爆雷,巨亏33亿晶圆代工厂力积电公布2025年第二季财报。第二季产能利用率升至75%,晶圆出货量40万片左右,季增8.67%,营收112.78亿新台币,季增1%。但因汇兑损失15.9亿元,净损33.34亿元。产能利用率从第1季73%,攀升至第2季75%,第2季晶圆出货量约40万片,季增8.67%。第2季营收新台币112.78亿元,季增1%,毛损率9%,净损33.34亿元,因汇兑损失15.9亿元。高压逻辑驱动芯片营收占比从第一季14%升至第二季17%,3D AI产品以硅中间层为主,第二季营收占比约2%。P5新厂月产能约8500片,计划下半年增加硅中间层产能,全年资本支出维持4.54亿美元。

下半年将聚焦DRAM代工、3D AI先进制程等高附加价值产品。总经理朱宪国提出,第3季订单能见度不高,但欧美电源管理芯片需求较强。展望下半年,DRAM代工因一线大厂退出8Gb DDR4市场,需求增长,投片产能满载,售价7月起逐月拉高,涨价效应滞后3-4个月。SLC Flash库存健康,客户下单意愿增高,24纳米产品新客户持续导入中。硅中介层方面,已进入量产开始贡献营收,以CoWoS-S为主,CoWoS-L提供客户导入设计。董事会日前通过扩增产能资本支出案,预期业绩贡献将逐步浮现。

06 智原推出DDR/LPDDR通用实体层IP

ASIC设计服务暨IP研发领导厂商智原科技,宣布推出第三至第五代DDR/LPDDR通用实体层IP。该IP适用于联电(UMC)22ULP与14FFC FinFET制程,广泛应用于多项SoC设计案中,经过验证,稳定性与兼容性符合JEDEC规范。智原致力于提供优化自有IP解决方案,帮助ASIC客户提高开发效率、增强产品成本竞争力并降低风险。22ULP PHY适用于对功耗敏感应用,电压低至0.8V,适用于行动装置、5G与物联网等领域。14nm PHY支持DDR5/LPDDR5,传输速率高达6400Mbps,具备参数调整机制、阻抗匹配校正与DFE等功能,保障信号传输品质与稳定性。

营运总监林世钦指出,随着SoC设计愈发复杂,市场对高效能与低功耗存储解决方案需求渐涨。智原拥有完整DDR/LPDDR IP解决方案,涵盖控制电路、实体层及子系统整合服务,助力客户加速设计进程、降低开发风险,满足先进应用设计需求。