发布时间:2025-12-07 来源:芯报告

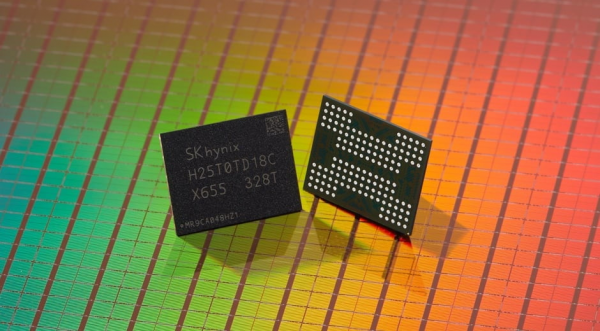

SK海力士正在研发混合键合工艺的300层NAND闪存,2027年量产。

继三星电子、YMTC和铠侠之后,SK海力士也计划提升在先进NAND闪存领域的竞争优势。

据透露,SK海力士300层第十代(V10)NAND闪存,计划明年通过测试线完成研发,2027年开始全面量产。

3D NAND的特点是芯片内部的存储元件垂直堆叠。

存储元件堆叠得越薄、层数越高,芯片的容量就越大。目前SK海力士量产的最高层数NAND闪存芯片拥有321层。

V10的关键在于引入了混合键合技术,将两片晶圆像单片晶圆一样键合在一起。

以NAND闪存为例,存储单元晶圆和外围电路晶圆是分别制造,然后再键合在一起的。

在V9(321层)NAND闪存之前,SK海力士一直采用单片晶圆同时制造存储单元和外围电路的方法。

这种方法被称为“PUC(Peri under Cell,单元下外围电路)”工艺,即将外围电路构建在晶圆的最底部,而存储元件堆叠在其上。

被困在晶圆底部的存储元件必须承受高温工艺,直到数百层堆叠完成。

随着NAND层数的增加,外围电路故障的可能性也增加。

采用混合键合技术不仅减轻外围电路的负担,而且通过分割两片晶圆生产的,缩短生产时间。

这是因为不同晶圆上的数百个芯片必须在纳米级精度上精确重叠并键合,从而实现无缝连接。

奥地利的EVG和日本的东京电子等公司在晶圆间混合键合设备方面实力雄厚。

业内预期SK海力士会从400层或更高层数的NAND闪存,开始采用混合键合技术。

由于主要竞争对手加速混合键合技术的商业化,威胁到SK海力士作为第二大厂商的地位,因此从300层的V10闪存开始采用。

首家将此工艺应用于NAND制造的公司是长江存储。Xtacking的混合键合技术在64层NAND闪存,2018年开始量产,迅速推进了先进NAND工艺的发展。

日本铠侠已将混合键合技术引入,并命名为CBA(CMOS直接键合阵列),2023年开始应用。

三星电子计划将混合键合技术,应用在即将量产的V10(400层)NAND闪存。

SK海力士明年将继续投资NAND业务,包括V10工艺的研发以及现有生产线向V9生产线的改造。

预计将在未来一年内将每月4万至6万片12英寸晶圆的产能转换为V9产能。

今年上半年还在囤积NAND闪存库存,但由于企业级SSD需求激增,工厂已满负荷运转。